# Development Circuit Under Test Technology For High Speed IC's Design

1.RR Swetha, Assistant Professor, 2.K.V.Divya, Assistant Professor 1,2.Department of EIE, RV College of Engineering, Bangalore, India. Swethar@rvce.edu.in

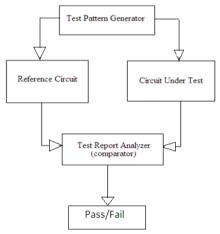

Abstract: Test Control piece is a testability method that places the testing capacities physically with the circuit under test (CUT). The control engineering requires the expansion of three pieces to an advanced circuit which are a test design generator, a reaction analyzer, and a test controller. The test design generator produces the test designs for the CUT. A counter is utilized as an example generator to produce the examples. A commonplace reaction analyzer is a comparator with put away reactions. It examines the test reactions to decide accuracy of the CUT. A test control square is important to initiate the test and break down the reactions. In any case, when all is said in done, a few test-related capacities can be executed through a test controller circuit. In this anticipate, the configuration is actualized by utilizing of a Counter. In the underlying state, the Counter yield will be set to 0. Later, on event of every clock, the worth will be augmented by 1, yet when the yield ranges to the estimation of 511, again the counter resets to 0. Along these lines the 9-bit counter is proficient to produce all conceivable Test designs. The examples created by the counter are connected to the UART (CUT).In the UART it is required to perform an expansion operation at one occasion. Along these lines, we actualized the expansion operation by utilizing Reversible Logic Gates. By utilizing this system, power utilization is diminished contrasted and ordinary adders. This anticipate is actualized by VERILOG HDL in Xilinx 12.3i with the gadget XC3S500E-5fg320. Keywords: CUT, Generator, Analyser

#### **I.INTRODUCTION**

Serial correspondence is the procedure of sending information and getting one piece of information at one time successively through an interchanges channel or PC transport. Then again, parallel correspondences is a procedure where every one of the bits of every image are sent together. By and large, serial correspondence is utilized for all long interchanges and most PC systems where it is unreasonable to utilize parallel correspondences because of the expense of link and synchronization. These days PC transports or system correspondence utilizing serial interchanges are turning out to be more basic as enhanced innovation empowers them to exchange information at higher speeds. There are 2 sorts of serial correspondence, full duplex and half duplex. A full duplex gadget can send and get information in the meantime. Accordingly, a full duplex correspondence needs 2 distinctive ports, one for serial in information while another for serial out information. Then again, half duplex serial gadgets bolster stand out way correspondences and accordingly just capable either accepting or transmitting information at once. Regularly half duplex gadgets have the same port for both serial in and out. Widespread nonconcurrent get transmit (UART) is an offbeat serial collector/transmitter. It is a bit of PC equipment that ordinarily utilized as a part of PC serial port to decipher information amongst information and transmits the individual bits in a consecutive manner. At the getting point, UART re-collects the bits into complete bytes. Offbeat transmission permits information to be transmitted without sending a clock sign to the recipient. Along these lines, the sender and collector must concur on timing parameters ahead of time and exceptional bits are added to every word, which is utilized to synchronize the sending and accepting units. By and large, UART contains of two fundamental piece, the transmitter and recipient square. The transmitter sends a byte

of information a little bit at a time serially out from UART while UART collector gets the serial in information a tiny bit at a time and changes over them into a byte of information. UART begins the information transmission by information that is to be transmitted. The Start Bit is additionally used to educate the recipient that a byte of information is going to be sent. After the Start Bit, the individual bits of the "byte" of information are sent, with the Least Significant Bit (LSB) being sent first. Every piece in the transmission is transmitted for the very same measure of time as the greater part of alternate bits. On the other, UART the recipient should test the rationale esteem that being gotten at around part of the way through the period doled out to every piece to figure out whether it is rationale 1 or rationale 0. When a byte of information has been sent, the transmitter may mistake checking may utilize the Parity Bit. In this anticipate, equality bit by the transmitter to show the transmitter has finished the information transmission. In the event that another byte of information is to be transmitted, the Start Bit for the new information can be sent when the Stop Bit for the past word has been sent.

### II.REVERSIBLE LOGIC GATES

Reversible rationale is a standout amongst the most indispensable issue at present time and it has distinctive regions for its application, those are low power CMOS, quantum figuring, nanotechnology, cryptography, optical registering, DNA registering, computerized signal handling (DSP), quantum spot cell automata, correspondence, PC design. It is unrealistic to acknowledge quantum registering without usage of reversible rationale. The fundamental reasons for outlining reversible rationale are to reduction quantum cost, profundity of the circuits and the quantity of junk yields. Reversible rationale has gotten extraordinary consideration in the late years in view of its primary

necessity in VLSI plan. It has wide applications in low power CMOS and Optical data handling, DNA processing, quantum calculation and nanotechnology. The warmth created because of the loss of one piece of data is little at room temperature yet when the quantity of bits is more as on account of fast computational works the warmth scattered by them will be large to the point that it influences the execution and results in the lessening of lifetime of the segments .Bennett demonstrated that vitality would not disseminate from a framework the length of the framework permits the propagation of the inputs from watched yields. Reversible rationale bolsters the procedure of running the framework both forward and in reverse. This implies reversible calculations can produce inputs from yields and can unpredictable back to any point in the calculation history. A circuit is said to be reversible if the information vector can be extraordinarily recuperated from the yield vector and there is a coordinated correspondence between its data and yield assignments, i.e. not just the yields can be extraordinarily decided from the inputs, additionally the inputs can be recouped from the yields.

Fig.1.proposed Test control Architecture

Reversibility in registering suggests that no data about the computational states can ever be lost, so we can recuperate any prior stage by processing in reverse or un-figuring the outcomes. This is termed as coherent reversibility. The advantages of legitimate reversibility can be increased when utilizing physical reversibility. Physical reversibility is a procedure that disseminates no vitality to warm. Totally impeccable physical reversibility is for all intents and purposes unachievable. Figuring frameworks radiate warmth when voltage levels change from positive to negative: bits from zero to one. The vast majority of the vitality expected to roll out that improvement is radiated as warmth. Instead of changing voltages to new levels, reversible circuit components will slowly move charge starting with one hub then onto the next. Along these lines, one can just hope to lose a moment measure of vitality on every move. Reversible figuring firmly influences computerized rationale plans. Reversible rationale components are expected to recuperate the condition of inputs from the yields. It will affect guideline sets and abnormal state programming dialects too. In the long run, these will likewise must be reversible to give ideal proficiency.

Superior chips discharging a lot of warmth force reasonable confinement on how far would we be able to enhance the execution of the framework. Reversible circuits that preserve data, by un processing bits as opposed to discarding them, will soon offer the main physically conceivable approach to continue enhancing execution. Reversible processing will likewise prompt change in vitality productivity. Vitality proficiency will on a very basic level influence the pace of circuits, for example, nano circuits and thusly the velocity of most figuring applications. To build the movability of gadgets again reversible figuring is required. It will let circuit component sizes to diminish to nuclear size cutoff points and thus gadgets will turn out to be more convenient. In spite of the fact that the equipment outline costs brought about in not so distant future might be high yet the force expense and execution being more predominant than rationale equipment cost in today's registering time, the need of reversible figuring can't be overlooked.

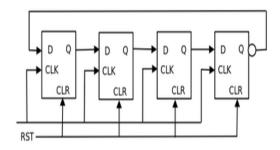

Fig.2.The Architecture for 9 bit counter.

A reversible rationale door is a n-information n-yield rationale gadget with balanced mapping. This decides the yields from the inputs furthermore the inputs can be remarkably recouped from the yields. Additionally in the amalgamation of reversible circuits direct fan-Out is not permitted as one-to-numerous idea is not reversible. However fan-out in reversible circuits is accomplished utilizing extra doors. A reversible circuit ought to be outlined utilizing least number of reversible rationale entryways. There are numerous number of reversible rationale doors that exist at present. The quantum expense of a 1x1 reversible door is thought to be zero while the quantum expense of a 2x2 reversible rationale entryway is taken as solidarity. The quantum expense of other reversible doors is computed by tallying the quantity of V, V+ and CNOT entryways present in their circuit. V is the square base of NOT entryway and V+ is its Hermitian. The V and V+ quantum doors have the accompanying properties:

$$V * V = NOT ....(1)$$

$V * V + = V + * V = 1 ....(2)$

$V + * V + = NOT ....(3)$

Peres entryway:

Peres entryway which is a 3\*3 door having inputs (A, B, C)

and yields P = A; Q = A XOR B; R = AB XOR C. It has Quantum taken a toll four.

HNG Gate:

The reversible HNG entryway can work independently as a reversible full snake. In the event that the data vector IV = (A, B, Cin, 0), then the yield vector gets to be OV = (P=A, Q=Cin, R=Sum, S=Cout).

Four Bit swell convey viper utilizing Vedic science:

Vedic arithmetic is the old Indian arrangement of science which for the most part manages Vedic scientific formulae and their application to different branches of math. Vedic science was recreated from the antiquated Indian sacred texts (Vedas) by Sri Bharati Krsna Tirtha after his exploration on Vedas . He built 16 sutras and 16 upa sutras after broad exploration in Atharva Veda. The most well known among these 16 are been found that Urdhva Tiryakbhayam is the most productive among these. The magnificence of Vedic arithmetic lies in the way that it decreases generally bulky looking computations in ordinary science to extremely straightforward ones. This is so in light of the fact that the Vedic formulae are asserted human personality works. Thus augmentations in DSP pieces can be performed at speedier rate. This is an extremely intriguing field and shows some viable calculations which can be connected to different branches of building.

Inputs a[0] and b[0] incorporating with 0 are given as inputs to PERES door and z0,s0 and k are taken as yields. The convey created from the peres entryway (k) is given as one of the inputs to HNG 1gate.S1 is taken as entirety bit and L as convey bit. The convey bit created from HNG 1 door is given as one to the inputs to HNG 2 entryway.

It creates test design for CUT. It will be devoted circuit or a miniaturized scale processor. Design created might be pseudo arbitrary numbers or deterministic succession. Here we are utilizing a 9 bit counter to generate arbitrary number. The Architecture for counter is as demonstrated as follows.

Tapping can be taken as we wish yet according to taping change the 9 bit counter yield produce will change and as we change in no of flip-flounder the likelihood of redundancy of irregular number will lessen. The underlying quality stacking to the 9 bit counter is known as seed worth.

Test Response Analyzer (TRA):

TRA will check the yield of cut and confirm with the reference circuit and give the outcome as mistake or not. Circuit under Test (CUT):

CUT is the circuit or chip in which we are going to apply reference circuit for testing stuck at zero or stuck at one mistake. In this paper the CUT is taken as UART.

Serial-in, parallel-out (SIPO):

This setup permits change from serial to parallel organization. Information is data serially. Once the information has been data, it might read off at every yield all the while.

SIPO registers are regularly joined to the yield of microchips when more yield pins are required than are accessible. This permits a few twofold gadgets to be controlled utilizing just a few pins - the gadgets being referred to are appended to the parallel yields, then the craved condition of every one of those gadgets can be conveyed of the microchip utilizing a solitary serial association.

PISO Additionally, PISO setups are ordinarily used to add more paired inputs to a microchip than are accessible - every double data (i.e. a switch or catch, or more convoluted hardware intended to yield high when dynamic) is joined to a parallel information.

##

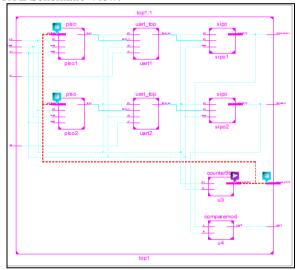

Fig. 3.Schematic View of the Top module.

RTL Schematic View:

Fig.4.RTL Schematic View of the Top module.

In the table the models are looked at regarding power, no of 4 data LUTS, delay and with memory. For the force figurings the gadget power 75.92mw and gadget accessible 4 data LUTS 9312 are taken as reference.

## IV.CONCLUSION

The proposed approach demonstrates the idea of creating the test designs utilizing 9 bit counter. The recreation results demonstrates that, how the examples are produced for the connected seed vector. This anticipate presents the execution concerning verilog dialect. Blending and usage (i.e. Interpret, Map and Place and Route) of the code is done on Xilinx - Project Navigator, ISE 12.3i suite. By this proposed design an IC can be tried effectively just by applying the test vectors. Specifically UART with reversible rationale is taken as CUT in this anticipate. By executing Adder with Reversible rationale, the force utilization is lessened from 0.49733mw to 0.47287mw when contrast and the typical snake for performing the expansion rationale.

## REFERENCES

[1] J. Ren and V. K. Semenov, "Progress with physically and

- logicallyreversible superconducting digital circuits," *IEEE Trans. Appl. Superconduct.*, vol. 21, no. 3, pp. 780–786, Jun. 2011.

- [2] S. F. Murphy, M. Ottavi, M. Frank, and E. DeBenedictis, "On thedesign of reversible QDCA systems," Sandia National Laboratories, Albuquerque, NM, Tech. Rep. SAND2006-5990, 2006.

- [3] H. Thapliyal and N. Ranganathan, "Reversible logic-based concurrentlytestable latches for molecular QCA," *IEEE Trans. Nanotechnol.*, vol. 9,no. 1, pp. 62–69, Jan. 2010.

- [4] P. Tougaw and C. Lent, "Logical devices implemented using quantum cellular automata," *J. Appl. Phys.*, vol. 75, no. 3, pp. 1818–1825, Nov.1994.

- [5] P. Tougaw and C. Lent, "Dynamic behavior of quantum cellularautomata," *J. Appl. Phys.*, vol. 80, no. 8, pp. 4722–4736, Oct. 1996.

- [6] M. B. Tahoori, J. Huang, M. Momenzadeh, and F. Lombardi, "Testingof quantum cellular automata," *IEEE Trans. Nanotechnol.*, vol. 3, no. 4,pp. 432–442, Dec. 2004.

- [7] G. Swaminathan, J. Aylor, and B. Johnson, "Concurrent testing of VLSIcircuits using conservative logic," in *Proc. Int. Conf. Comput. Design*, Cambridge, MA, Sep. 1990, pp. 60–65.

- [8] E. Fredkin and T. Toffoli, "Conservative logic," *Int. J. Theor. Phys.*, vol. 21, nos. 3–4, pp. 219–253, 1982.

- [9] P. Kartschoke, "Implementation issues in conservative logic networks," M.S. thesis, Dept. Electr. Eng., Univ. Virginia, Charlottesville, 1992.

- [10] G. Swaminathan, "Concurrent error detection techniques using parity," M.S. thesis, Dept. Electr. Eng., Univ. Virginia, Charlottesville, 1989.

- [11] H. Thapliyal, M. B. Srinivas, and M. Zwolinski, "A beginning in thereversible logic synthesis of sequential circuits," in *Proc. Int. Conf. Military Aerosp. Program. Logic Devices*, Washington, DC, Sep. 2005,pp. 1–5.

- [12] S. Mahammad and K. Veezhinathan, "Constructing online testablecircuits using reversible logic," *IEEE Trans. Instrum. Meas.*, vol. 59,no. 1, pp. 101–109, Jan. 2010.

- [13] H. Thapliyal and N. Ranganathan, "Design of reversible sequential circuits optimizing quantum cost, delay and garbage outputs," *ACM J.Emerg. Technol. Comput. Syst.*, vol. 6, no. 4, pp. 14:1–14:35, Dec.