# Implementation of H.264/Mpeg-4 Advanced Video Coding Standard

A.Princy<sup>1</sup>, C.Sridhar<sup>2</sup>

<sup>1</sup>PG Scholar, <sup>2</sup>Assistant Professor Electronics and Communication Engineering S.K.R Engineering college, Chennai, India. <sup>1</sup>princy6493@gmail.com, <sup>2</sup>Sri.induss@gmail.com

Abstract: H.264/AVC is newest video coding standard of the ITU-T Video Coding Experts Group and the ISO/IEC Moving Picture Experts Group. The main goals of the H.264/AVC standardization effort have been enhanced compression performance and provision of a "network-friendly" video representation addressing "conversational" (video telephony) and "nonconversational" (storage, broadcast, or streaming) applications.mH.264/AVC has achieved a significant improvement in rate-distortion efficiency relative to existing standards. This article provides an overview of the technical features of H.264/AVC, describes profiles and applications for the standard, and outlines the history of the standardization process. It covers all common video applications ranging from mobile services and videoconferencing to IPTV, HDTV, and HD video storage. This article discusses the technology behind the new H.264/MPEG4-AVC standard, focusing on the main distinct features of its core coding technology and its first set of extensions, known as the fidelity range extensions. In addition, this article also discusses the current status of adoption and deployment of the new standard in various application areas.

Keywords- Advanced video codec, H.264, High Definition, MPEG-4, Standard Definition.

# I. INTRODUCTION

Video processing systems require high performance processing elements and an efficient memory hierarchy design to reach real -time performance in the decoding of high definition video sequences. This is describes the design methodology for H.264/AVC video codec. The system architecture and scheduling will be addressed. The design consideration and optimization for its significant modules including bandwidth optimized motion compensation engine, reconfigurable intra predictor generator, low bandwidth parallel integer motion estimation will be mentioned. Due to the complex, sequential, and highly data-depended characteristics of all essential algorithms in H.264/AVC, not only the pipeline structure but also efficient memory hierarchy is required. The design case with a hybrid task pipelining scheme, a balanced schedule with block-level, MB-level, and frame-level pipelining, will be presented. By combining with many bandwidth reduction techniques and data reused schemes, very efficient architecture and implementation for plate-form based system is proved by the prototype chips. H.264/AVC is the newest international video coding standard. By the time of this publication, it is expected to have been approved by ITU-T as Recommendation H.264 and by ISO/IEC as International Standard 14 496-10 (MPEG-4 part10) Advanced Video Coding (AVC). The MPEG-2 video coding standard (also known as ITU-T H.262), which was developed about ten years ago prim airily as an extension of prior MPEG-1video capability with support of interlaced video coding, was an enabling technology for digital television systems worldwide. It is widely used for the transmission of standard definition (SD) and high definition (HD) TV signals over satellite, cable, and terrestrial emission and the storage of high-quality SD video signals onto DVDs. However, an increasing number of services and growing popularity of high definition TV are creating greater needs for higher coding efficiency. Moreover, other transmission media such as Cable Modem, xDSL, or UMTS offer much lower data rates than broadcast channels, and enhanced coding efficiency can enable the transmission of more video channels or higher quality video representations within existing digital transmission capacities. Video Coding Experts Group (VCEG) ITU-T SG16 Q.6 issued a call for proposals on a project called H.26L, with the target to double the coding efficiency (which means halving the bit rate necessary for a given level of fidelity) in comparison to any other existing video coding standards for a broad variety of applications. The first draft design for that new standard was adopted in October of 1999. In December

ICGPC16 538

www.scientistlink.com/ijeecc

of 2001, VCEG and the Moving Picture Experts Group (MPEG) ISO/IEC JTC 1/SC 29/WG 11 formed a Joint Video Team (JVT), with the charter to finalize the draft new video coding standard for formal approval submission as H.264/AVC.

#### II. **OVERVIEW OF H.264/AVC**

The architecture considers a four-level memory hierarchy composed of local SRAM memories and by off-chip DRAM memories. Off-chip DRAM memories can guarantee the necessary storage capacity at low cost if compared to embedded SRAM. The memory controller is designed with a multichannel data interface because different processing modules need to share the same data port. The multichannel controller manages data access requests and optimizes the reference memory utilization, enabling data processing modules to interact efficiently in order to satisfy the performance requirements.

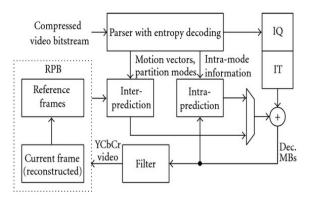

Fig1.Block diagram of H.264/AVC

The hardware implementation of the emerging H.264/AVC video compression standard presents a number of difficult challenges when it comes to real-time encoding at HDTV rates. It describes an efficient implementation of a baseline H.264/AVC encoder core capable of encoding a 1920x1080 video stream in real time at 30 frames per second (HDTV 1080p). A very favourable comparison with the JM 8.6 software reference model also will be presented. While the specific target of the design was HDTV 1080p, the small size and low clock frequency required make this core suitable for a variety of applications, from mobile communication devices to HDTV camcorders and video surveillance systems. Parsing with entropy decoding extracts from the compressed video bitstream the syntax elements to interframe and intraframe video reconstruction and compressed residual data. The residual data is decoded using fixed or variable length binary codes in the entropy parsing module and is processed in the inverse transform and inverse quantization (IT and IQ) steps. Using information decoded from the bitstream, the decoder creates a prediction block using intra or inter prediction modes. Motion compensation (MC) is the hardware module which reconstructs an actual frame from reference frames. Intra prediction reconstructs each image block from its neighbourhood.

The core needs an external memory to store the previous frame and the current frame being reconstructed. Also, chances are that it will be used in a SoC environment where other cores and a CPU might need to share the same resource. Therefore designed the core with that goal in mind. The characteristics of the memory interface are:

- Very similar to and easy to integrate with the AMBA™ AHB interface

- Tolerant of high latencies and delays typical of shared buses

- SDRAM aware

Can be clocked at a different clock speed from the main core

| Sequence name | Frame size | No. of frames | File size (bytes) |

|---------------|------------|---------------|-------------------|

| Mobile        | 352 x 288  | 300           | 4,56,19,200       |

| Tempted       | 352 x 288  | 260           | 3,95,36,640       |

| Tennis        | 720 x 480  | 300           | 15,55,20,000      |

Table 1. The sequences used in the test

Indian Journal of Emerging Electronics in Computer Communications, Volume.3, Issue.1, 2016, Page.538-541 www.scientistlink.com/ijeecc

Local and off-chip memory resources used by the multichannel memory controller, grouped within the levels of the memory hierarchy. It contains the following four levels.

**Level 3:** Off-chip DRAM memory: it is the biggest memory module with reduced cost if compared with the internal SRAM memory. This level has the larger latency.

Level 2: Memory controller buffer: it is the memory level used to store data for an off-chip memory transfers. Data is saved along with addresses and commands to be written in external memory. This memory level allows the controller (PHY) to manage off-chip memory information with auto refresh operations and different banks or row changing without disrupting the interfaces that are accessing data. The Read FIFO is only used with additive read latency (AL) option is enabled.

**Level 1:** Macroblock-level memory: in this level, data is stored in buffers until reach the minimum size of a macroblock before being transferred to external memory. This level is necessary to maximize the size of data transfer to external memory, because the transfer takes the form of bursts of data in line memory address.

**Level 0:** Local SRAM processing buffers: it is the lowest level of memory, characterized by local memory in the processing units used to process information locally, it enables the execution of more local processing without external memory access.

#### III. MPEG-4 SYSTEM

The Motion Picture Expert Group (MPEG) has successfully introduced two standards for coding of audio visual information, known by the acronyms MPEG-1 and MPEG-2. The first addresses the storage of audio visual information on CD-ROM, whereas the second handles the generic coding of digital TV and HDTV signals. The most important goal of both the MPEG-1 and MPEG-2 standards was to make the storage and transmission of digital audio visual material more efficient, through the use of compression techniques. To achieve this, both deal with frame-based video and audio. Interaction with the content is limited to the video frame level, with its associated audio.

H.264 or MPEG-4 is a Advanced Video Coding (MPEG-4 AVC) is a video coding format that is currently one of the most commonly used formats for the recording, compression, and distribution of video content. The final drafting work on the first version of the standard was completed in May 2003, and various extensions of its capabilities have been added in subsequent editions. H.264/MPEG-4 AVC is a block-oriented motion-compensation-based video compression standard developed by the ITU-T Video Coding Experts Group (VCEG) together with the ISO/IEC JTC1 Moving Picture Experts Group (MPEG). The project partnership effort is known as the Joint Video Team (JVT).

The intent of the H.264/AVC is to create a standard capable of providing good video quality at substantially lower bit rates than previous standards (i.e., half or less the bit rate of MPEG-2, H.263, or MPEG-4 Part 2), without increasing the complexity of design so much that it would be impractical or excessively expensive to implement. An additional goal was to provide enough flexibility to allow the standard to be applied to a wide variety of applications on a wide variety of networks and systems, including low and high bit rates, low and high resolution video, broadcast, DVD storage, RTP/IP packet networks, and ITU-T multimedia telephony systems.

# 3.1 MPEG-4 Audio

MPEG-4 Audio covers the complete bitrate range from 2 to 64 kbit/s per channel. Acceptable speech quality is obtained already at 2kbit/s and transparent quality of monophonic music sampled at 48 kHz at 16 bits per sample is obtained at 64 kbit/s. Appealing quality is obtained at 16 kbit/s for stereo music. 24 kbit/s is the bitrate used by Digital Radio of conventional AM radio. Scalable audio is supported for Internet applications with uncertain access bandwidth.

### 3.2 MPEG-4 Video

MPEG-4 Visual provides a natural video coding algorithm that is capable of operating from 5 kbit/s upwards to transparent quality. One important feature of the Visual part of MPEG-4 is the ability to code not just a rectangular array of pixels, but also "object" with arbitrary shape, such as a walking person or a moving car in a scene. The object can also be of synthetic origin.

Princy et.al 540

#### IV RESULTS

The inclusion of this memory hierarchy has to be considered in the system design. It is known that buffering on lower levels of the hierarchy reduces potential bottlenecks in higher levels, where channel multiplexing is needed. Also, the sequential access characteristics of a video recovering task benefits from burst readings in DDR memory. Strategies were presented and analyzed to enable IP reuse and integration by buffering data and controlling processing on modules. The strategies proved to be effective, as the expected performance of the system was not reduced, and they introduced a small overhead in the architecture of the final system.

Complexity grows with the size of a system, and so does the time for design synthesis and validation. It has a strong impact on development time. In this work, the strategy of incremental integrations was crucial for reducing SoC complexity and verification effort, enabling to specify clear checkpoints in the development. Use the Video Reader function with the read method to read video data from a file into the MATLAB.

## V CONCLUSION

The emerging H.264/AVC video coding standard has been developed and standardized collaboratively by both the ITU-T VCEG and ISO/IEC MPEG organizations. H.264/AVC represents a number of advances in standard video coding technology, in terms of both coding efficiency enhancement and flexibility for effective use over a broad variety of network types and application domains. Its VCL design is based on conventional block-based motion-compensated hybrid video coding concepts, but with some important differences relative to prior standards. We thus summarize some of the important differences:

- enhanced motion-prediction capability;

- use of a small block-size exact-match transform;

- adaptive in-loop deblocking filter;

- enhanced entropy coding methods.

When used well together, the features of the new design provide approximately a 50% bit rate savings for equivalent perceptual quality relative to the performance of prior standards (especially for higher-latency applications which allow some use of reverse temporal prediction).

# REFERENCES

- [1] G. J. Sullivan, J. Ohm, W.-J. Han, and T. Wiegand, "Overview of the high efficiency video coding (heve) standard," Circuits and Systems for Video Technology, IEEE Transactions on, vol. 22, no. 12, pp. 1649–1668, 2010.

- [2] "Draft ITU-T recommendation and final draft international standard of joint video specification (ITU-T Rec. H.264/ISO/IEC 14 496-10 AVC," in Joint Video Team (JVT) of ISO/IEC MPEG and ITU-T VCEG, JVTG050,2003.

- [3] "Generic Coding of Moving Pictures and Associated Audio Information Part 2: Video," ITU-T and ISO/IEC JTC 1, ITU-T Recommendation H.262 and ISO/IEC 13 818-2 (MPEG-2), 1994.

- [4] Martinus Johannes Pieter Berkho "Analysis and Implementation of the H.264 CABAC entropy decoding engine", Computer Engineering Mekelweg 4, Thesis Master of Science, The Netherlands (2012).

- [5] "Video Coding for Low Bit Rate Communication," ITU-T, ITU-T Recommendation H.263 version 1, 1995.

- [6] "Coding of audio-visual objects-Part 2: Visual," in ISO/IEC 14 496-2 (MPEG-4 Visual Version 1), Apr. 1999